1. Verdrahtungsplan

Das LC-Meter wurde als ein Prototyp entworfen bestehend aus je einem Block für

- eine CPU mit I/O-Ports

- einen freischwingenden LC-Oszillator für die L- und C-Messung

- einen monostabilen Multivibrator (Monoflop) für die C-Messung

- ein LC-Display

- und ein paar Bedientasten

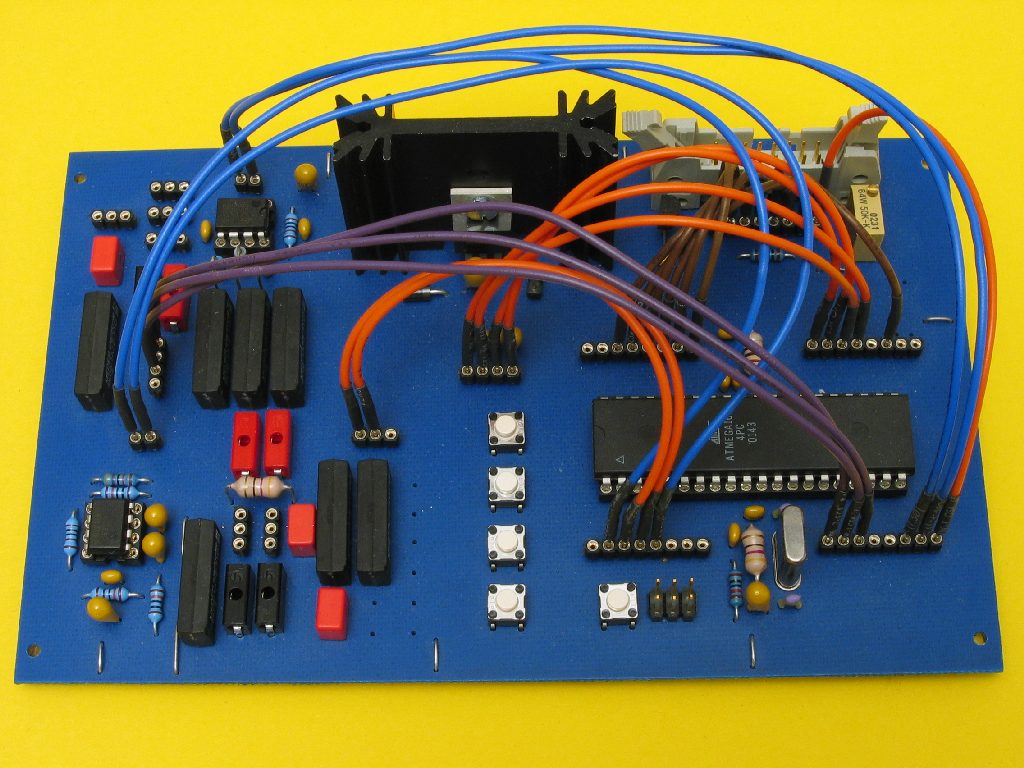

Auf der Platine sind diese Blöcke - von der Stromversorgung einmal abgesehen - nicht untereinander verbunden, um leichter experimentieren zu können. Die Verdrahtung erfolgte durch Steckbrücken. Mittlerweile hat sich eine bestimmte Verdrahtung herauskristallisiert, die auch auf dem folgenden Bild zu sehen ist. Auch bei den Relais hat sich das ein oder andere als nicht notwendig herausgestellt, so daß es nicht mehr bestückt werden braucht. Einzelheiten datzu folgen weiter unten.

Es ist jedoch nicht leicht, die Verbindungen nur aufgrund dieses Bildes zu rekonstruieren. Daher im folgenden eine Tabelle, die die genaue Verdrahtung angibt.

| Port | von Buchsenleiste und Pin | nach Buchsenleiste und Pin | Funktion |

|---|---|---|---|

| A0 | JP5 - 1 | JP1 - 8 | LCD: DB7 |

| A1 | JP5 - 2 | JP1 - 7 | LCD: DB6 |

| A2 | JP5 - 3 | JP1 - 6 | LCD: DB5 |

| A3 | JP5 - 4 | JP1 - 5 | LCD: DB4 |

| A4 | JP5 - 5 | JP1 - 2 | LCD: RS |

| A5 | JP5 - 6 | JP1 - 3 | LCD: R/-W |

| B1 | JP2 - 7 | JP11 - 1 | LC-Oszillator: HF-out |

| B2 | JP2 - 6 | JP6 - 2 | LC-Oszillator: K1, Kurzschluß über L3 |

| B3 | JP2 - 5 | JP6 - 3 | LC-Oszillator: K2, 330 pF |

| B4 | JP2 - 4 | JP11 - 2 | LC-Oszillator: K7, Kurzschluß über Lx |

| C2 | JP3 - 6 | JP1 - 4 | LCD:E |

| C4 | JP3 - 4 | JP12 - 4 | Taster S6 |

| C5 | JP3 - 3 | JP12 - 3 | Taster S5 |

| C6 | JP3 - 2 | JP12 - 2 | Taster S4 |

| C7 | JP3 - 1 | JP12 - 1 | Taster S3 |

| D0 | JP4 - 8 | JP10 - 3 | Monoflop: K4, 1 kΩ |

| D1 | JP4 - 7 | JP10 - 2 | Monoflop: K5, 33 kΩ |

| D2 | JP4 - 6 | JP10 - 1 | Monoflop: K6, 1 MΩ |

| D5 | JP4 - 3 | JP9 - 1 | Monoflop: Trigger (Start) |

| D6 | JP4 - 2 | JP9 - 2 | Monoflop: Q (Pulsausgang) |

| D7 | JP4 - 1 | JP1 - 1 | LCD: Beleuchtung |

Die Lage des Pin 1 ist leider nicht konsequent gewählt. Hier eine Übersicht. Dazu legt man die Platine so hin, daß die Bestückungsseite sichtbar ist und daß der Prozessor in der rechten Hälfte ist. Also - wie bei obigem Bild.

| Buchsenleiste | Lage von Pin 1 | Funktion |

|---|---|---|

| JP1 | rechts | LCD |

| JP2 | rechts | Port B |

| JP3 | links | Port C |

| JP4 | rechts | Port D |

| JP5 | rechts | Port A |

| JP6 | rechts | LC-Oszillator: Relais |

| JP10 | oben | Monoflop: Relais |

| JP11 | links | LC-Oszillator: Ausgang und Relais |

| JP12 | rechts | Taster |

2. Modifikationen und andere Abweichungen vom Schaltplan

Im folgenden habe ich nochmal die Abweichungen der aktuellen Lösung vom Schaltplan bzw. Layout zusammengefaßt, die sich im Laufe der Zeit ergeben haben. Das Programm verlangt, daß diese Abweichungen/Modifikationen berücksichtigt werden. Der Hauptartikel und die Schaltplanauszüge darin berücksichtigen bereits diese Änderungen.

- LC-Oszillator: Das Relais K1 dient jetzt zur Überbrückung von L3, während es im Schaltplan noch dazu dient, den 330 pF Kondensator C14 zu schalten. Der Kondensator C14 wird nicht bestückt. Diese Modifikation ist unten nochmal genauer erklärt.

- LC-Oszillator: Der Kondensator C15 mit 100 pF bei Relais K2 wird entfernt und stattdessen der 330 pF Kondensator (ehemals C14) eingelötet.

- LC-Oszillator: K8 und C28 werden nicht angesteuert und können daher entfallen.

- Monoflop: K3, das einen 100 pF Kondensator parallel zur unbekannten Kapazität Cx schaltet, wird nicht benötigt.

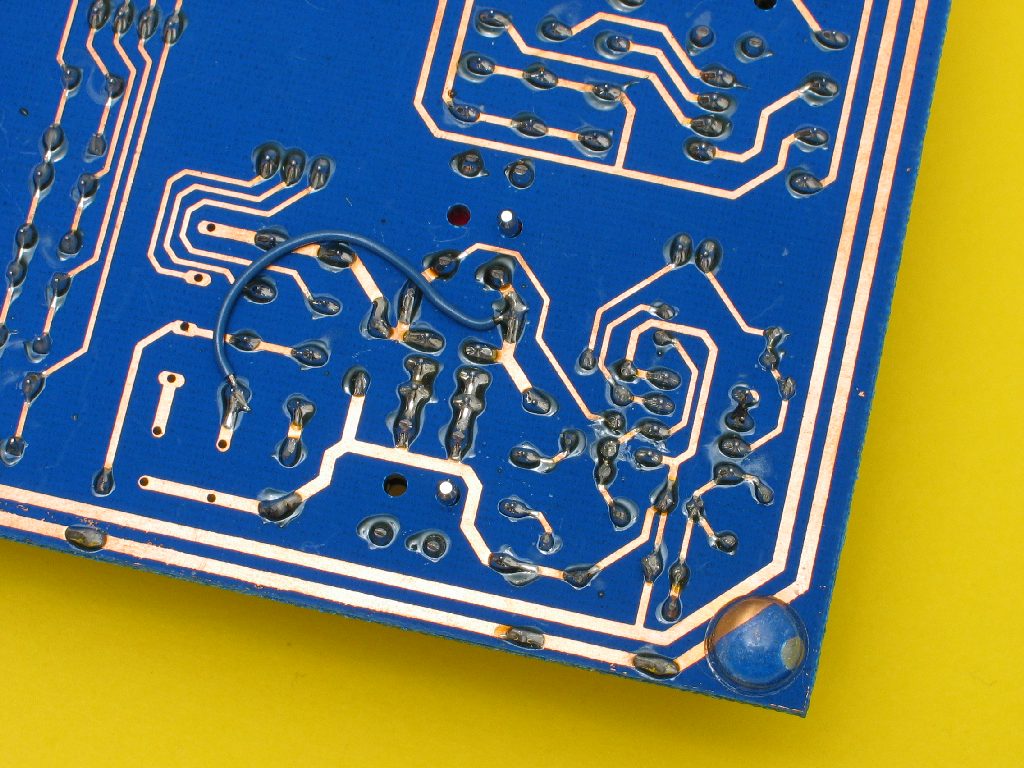

Hier nochmals die Modifikation im Umfeld des Relais K1: Der Kondensator C14 bei K1 wird nicht bestückt. Stattdessen wird die Leiterbahn, die K1 mit dem Kondensator verbunden hätte, jetzt mit der linken Seite (von der Bestückungsseite aus gesehen) von L3 (47 μH) verbunden. Damit kann K1 nun L3 kurzschließen. Das folgende Bild zeigt die Modifikation, die leicht mit einem Stück Draht durchzuführen ist. Leiterbahnen müssen nicht unterbrochen werden: